Rangkaian Decoder dan Jenis-Jenisnya - Sesuai dengan namanya, sebuah decoder merupakan jenis rangkaian logika yang mengkodekan kembali sebuah input. Beberapa referensi menyebutnya dengan istilah binary decoder, hal tersebut dikarenakan kombinasi input maupun output di implementasikan oleh tipe data biner yakni 0 dan 1.

|

Rangkaian Logika Decoder dan Jenis-Jenisnya

|

Apabila diberikan kode biner n-bit, maka rangkaian decoder akan mengkonversinya sebanyak 2^n kemungkinan kode yang dapat digunakan. Sebuah decoder akan menentukan satu dari beberapa keluaran (2^n output) dengan cara mengkodekan kembali (mengkonversi) nilai-nilai biner masukan (n input). Rangkaian decoder akan membuat semua kemungkinan dari variabel n input. Namun hanya ada satu output yang akan aktif untuk setiap kombinasi input. Terdapat tiga kemungkinan kombinasi yang digunakan dalam rangkaian decoder :

- Menggunakan mode active-high, pada mode ini output akan diatur dalam kondisi active-high. Output yang dihasilkan, hanya ada satu output bernilai aktif pada masing-masing kombinasi input.

- Menggunakan mode active-low, berbanding terbalik dengan mode active-high, pada mode ini output di set ke dalam kondisi active-low. Output yang dihasilkan, akan ada 1 output yang bernilai 0 (low), sedangkan lainnya bernilai 1. Hal tersebut berlaku untuk semua kombinasi input.

- Mode active-high enable, pada mode ini input dibagi menjadi 2, yakni enabled untuk input bernilai 1 dan disabled untuk input bernilai 0. Kondisi enabled terdiri dari 4 kombinasi input (untuk 2 to 4 decoder), sedangkan pada kondisi disabled akan bernilai 0 dengan kombinasi input di abaikan.

- Output pada kondisi enabled sama halnya dengan mode active-high, yakni hanya terdapat 1 output bernilai 1 (high) dari keempat output (2 to 4 decoder) yang berlaku bagi kesemua kombinasi input. Sedangkan pada kondisi disabled, kesemua output bernilai 0 (low).

- Mode active-low enable, merupakan kebalikan dari mode active-high enable. Pada praktinya juga terbagi menjadi 2, yakni enabled untuk 4 kombinasi input (2 to 4 decoder) dan disabled bagi input yang di abaikan. Pada mode active-low enable, kondisi enabled bernilai 0 sedangkan disabled bernilai 1.

Jenis-Jenis Rangkaian Decoder

Decoder dapat dibuat menggunakan rangkaian gerbang AND atau OR, dengan ketentuan jumlah input lebih kecil dari jumlah output (N inputs < 2^n outputs). Terdapat beberapa tipe decoder yang biasa digunakan, diantaranya decoder 1 to 2, decoder 2 to 4, decoder 3 to 8, hingga rangkaian logika decoder 4 to 16. Masing-masing tipe mulai dari rangkaian, tabel kebenaran dan IC (Integrated Circuit) yang digunakan akan diperinci pada penjelasan berikut.

Decoder 1 to 2

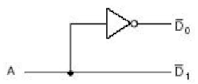

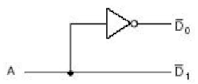

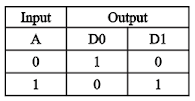

Tipe decoder 1 to 2 merupakan jenis decoder 1 input dengan jumlah output 2^1. Rangkaian yang digunakan 1 jalur menggunakan inverter. Berikut merupakan gambar rangkaian, tabel kebenaran dan IC (Integrated Circuit) yang berlaku untuk decoder 1 to 2.

|

| Rangkaian Logika Decoder 1 to 2 |

|

| IC Decoder 1 to 2 |

|

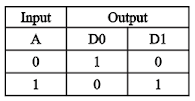

| Tabel Kebenaran Decoder 1 to 2 |

Decoder 2 to 4

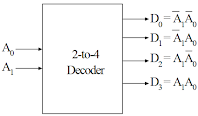

- D0 = A1’ A0’ (minterm m0) di implementasikan dalam input 00

- D1 = A1’ A0 (minterm m1) di implementasikan dalam input 01

- D2 = A1 A0’ (minterm m2) di implementasikan dalam input 10

- D3 = A1 A0 (minterm m3) di implementasikan dalam input 11

Pada gambar decoder 2 to 4 menunjukkan rangkaian menggunakan gerbang AND dan NOT sebagai inverter. Pada rangkaian tersebut pula menunjukkan jika output yang dihasilkan merupakan hasil dari kombinasi minterm 1 (D0) sampai dengan minterm 4 (D3).

Input “Enable” dalam Decoder

Secara umum, rangkaian decoder memiliki input “enable”. Input “enable” memungkinkan tidak ada logika operasi, namun hanya bertanggung jawab terhadap status decoder, yakni aktif atau tidak aktif.

Beberapa kemungkinan apabila input berstatus E (enable) :

- Apabila bernilai nol (aktif), maka semua output akan bernilai nol terlepas dari kombinasi input

- Apabila bernilai satu (tidak aktif), maka decoder akan melakukan operasi normal

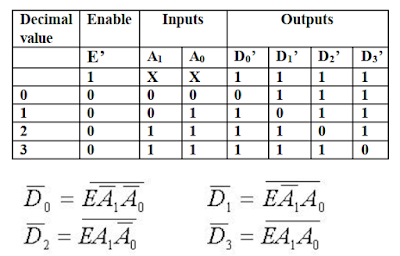

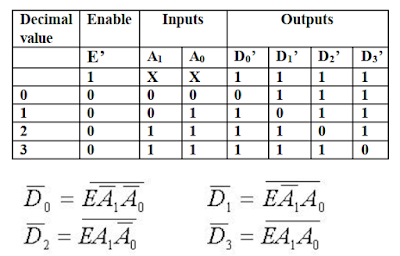

sebagai contoh, di sajikan rangkaian decoder 2 to 4 dengan enable input. Perlu diperhatika kembali bahwasanya enable input hanya bertanggung jawab untuk mengaktifkan decoder. Apabila Enable E bernilai nol, maka semua output decoder akan bernilai nol pula, terlepas dari kombinasi input A1 dan A0. Namun, jika Enable E bernilai 1, maka decoder akan melakukan operasi normal. Seperti digambarkan pada tabel kebenaran berikut.

|

| Tabel Kebenaran Decoder 2 to 4 dengan Enable |

Decoder 3 to 8

Pada decoder 3 to 8 terdapat sejumlah tiga input dan delapan output. Tiga input akan ditransformasikan kedalam delapan output. Adapun input dan output yang digunakan merupakan jenis bilangan biner yang dikombinasikan satu sama lain. Kombinasi input yang sesuai akan dapat mengaktifkan jalur output.

|

| IC Decoder 3 to 8 |

Setiap output merepresentasikan satu minterm. Seperti dijelaskan sebelumnya bahwa minterm merupakan rangkaian kombinasi input yang dapat menghasilkan output dalam sistem digital. Apabila terdapat kombinasi A2 A1 A0 = 001, maka output D1 akan bernilai 1, sementara jalur output lain akan bernilai 0, dst.

|

| Rangkaian Logika Decoder 3 to 8 |

Perlu diperhatikan bahwa pada kondisi normal, hanya 1 jalur output yang dapat diaktifkan. Sehingga dari rule tersebut dapat kita ketahui bahwa dari berbagai kombinasi input hanya menghasilkan satu jalur yang sesuai yang akan diaktifkan.

|

| Tabel Kebenaran Decoder 3 to 8 |

Setiap kombinasi input akan mewakili satu minterm. Terlihat pada tabel kebenaran decoder 3 to 8, didalamnya terdiri dari delapan fungsi output, dari D0 hingga D7. Masing-masing fungsi tersebut mewakili satu minterm. Dengan demikian fungsi D0 sebagai hasil dari minterm A2’ A1’ A0’, demikian pula pada fungsi D7 adalah A2 A1 A0. Jika kita perhatikan pada gambar, terdapat tiga inverter yang menyediakan komplemen input. Kesemuanya menggunakan gerbang AND yang kemudian merepresentasikan sebuah minterm. Hal tersebut juga memungkinkan adanya penambahan input enable pada rangkaian decoder ini.

Membuat Rangkaian Decoder dengan Gerbang NAND

beberapa decoder dapat dibangun menggunakan gerbang logika NAND. Bedanya pada rangkaian ini semua output rangkaian decoder akan bernilai 1, lain dari pada itu outputnya akan bernilai 0. Berikut ini merupakan contoh tabel kebenaran decoder 2 to 4 menggunakan gerbang NAND.

|

| Tabel Kebenaran Decoder 2 to 4 menggunakan gerbang NAND |

Rangkaian decoder ini dapat dibangun menggunakan enable, seperti halnya yang telah dijelaskan sebelumnya pada decoder menggunakan gerbang AND. Tabel kebenaran disajikan pada tabel berikut, perhatikan bahwa minterm merupakan bentuk komplemen.

|

| Rangkaian Logika Decoder 2 to 4 dengan Enable menggunakan gerbang NAND |

Rangkaian decoder 2 to 4 dengan enable input yang dibangun menggunakan gerbang NAND ditunjukkan pada gambar diatas. Rangkaian ini beroperasi dengan output berkomplemen dan input enable E juga berkomplemen guna mencocokkan dan menyesuaikan output dari rangkaian decoder gerbang NAND. Decoder akan diaktifkan apabila E bernilai nol. Seperti yang terlihat pada tabel kebenaran, hanya ada satu output yang dapat bernilai 0, sedangkan jalur output lain akan bernilai 1. Output 0 direpresentasikan oleh minterm A1 dan A0. Rangkaian akan berstatus tidak aktif manakala E bernilai 1, terlepas dari nilai kombinasi kedua input. Apabila rangkaian di disable (non aktif), tidak akan ada output bernilai 0 dan tidak akan ada minterm yang dipilih. Kombinasi logika input dan output tersebut disajikan pada tabel berikut.

|

| Tabel Kebenaran Decoder 2 to 4 dengan Enable menggunakan gerbang NAND |

Demikian penjelasan kali ini yang membahas tentang rangkaian decoder dan jenis-jenisnya. Jika ada kesalahan maupun masukan dapat disampaikan melalui laman komentar dibawah. Jangan lupa untuk tetap update postingan-postingan Kelas Informatika dengan mengikuti fanspage kami. Salam 😊

Maaf, saya mau bertanya untuk tanda X di tabel itu artinya apa ya? Terima kasih

BalasHapustanda "x" dalam tabel kebenaran rangkaian logika berarti "tetap" atau "tidak ada perubahan"

Hapus